## CONVERSION A/N et N/A

## 2.CONVERSION NUMERIQUE-ANALOGIQUE

### CONVERSION NUMERIQUE-ANALOGIQUE

- · Convertisseurs potentiométriques

- · Convertisseurs à résistances pondérées

- · Convertisseurs à échelle R/2R et M/2M

- Convertisseurs à sources de courant pondérées

- Exercice(CMOS R-2R DAC)

- · Convertisseurs à capacités pondérées

- · Convertisseurs sur-échantillonnés

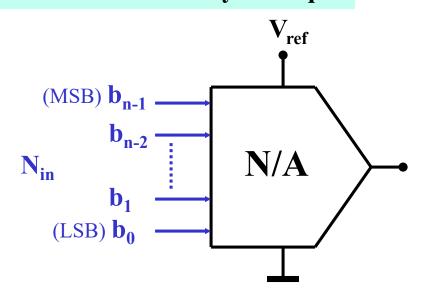

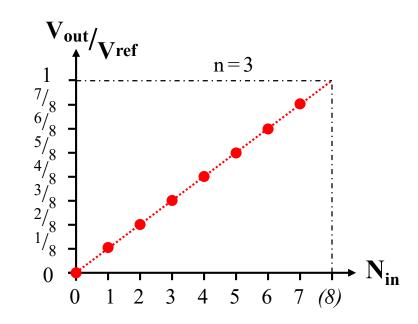

### CONVERTISSEURS N/A

#### Définition et schéma symbolique

$$V_{out} = \frac{V_{ref}}{2^n} \cdot \sum_{i=0}^{n-1} b_i \cdot 2^i = \frac{V_{ref}}{2^n} \cdot N_{in}$$

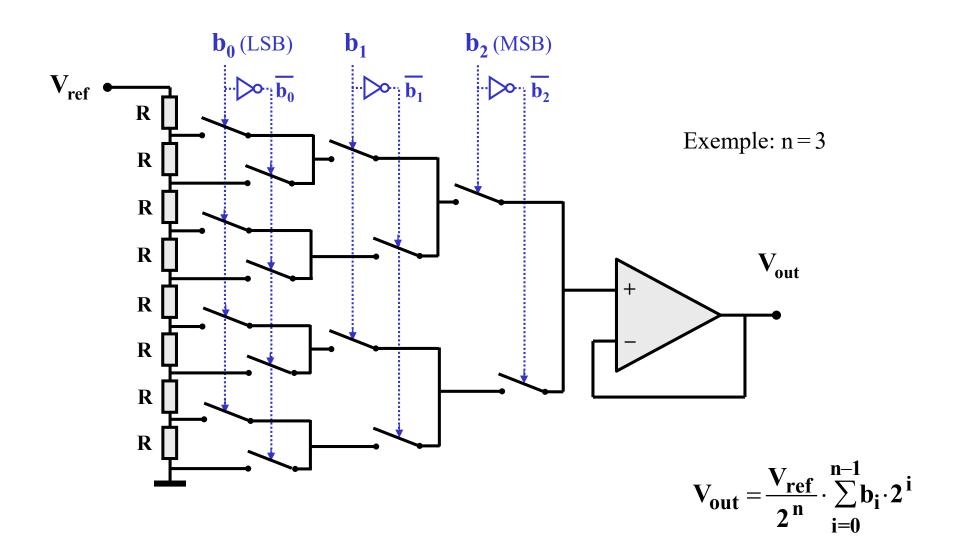

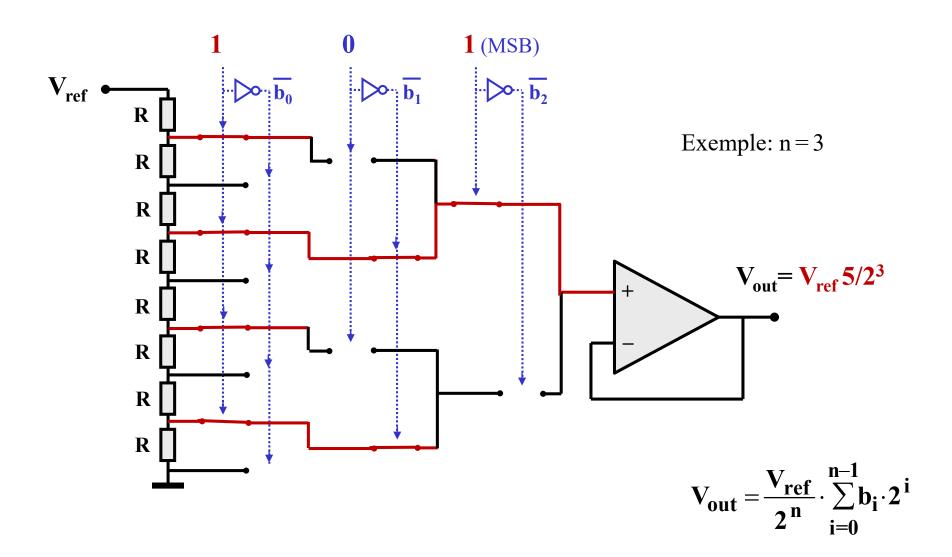

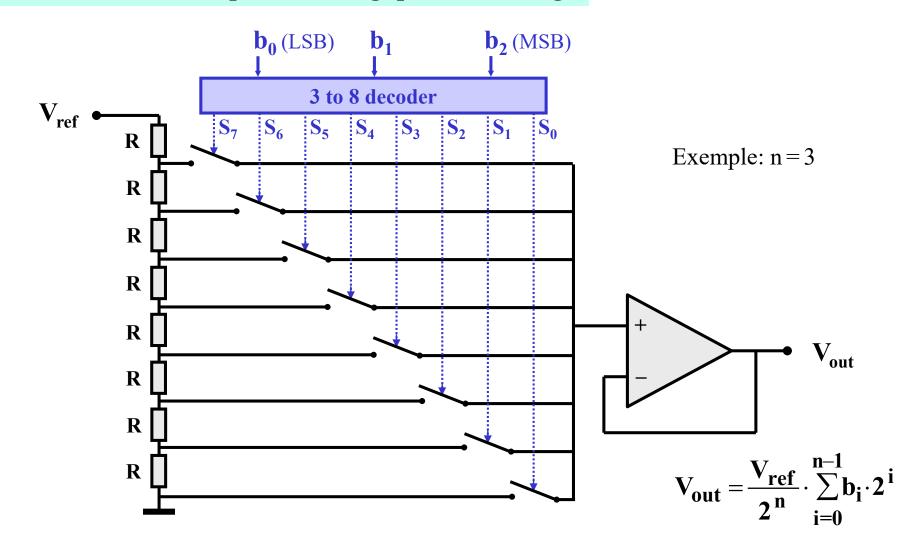

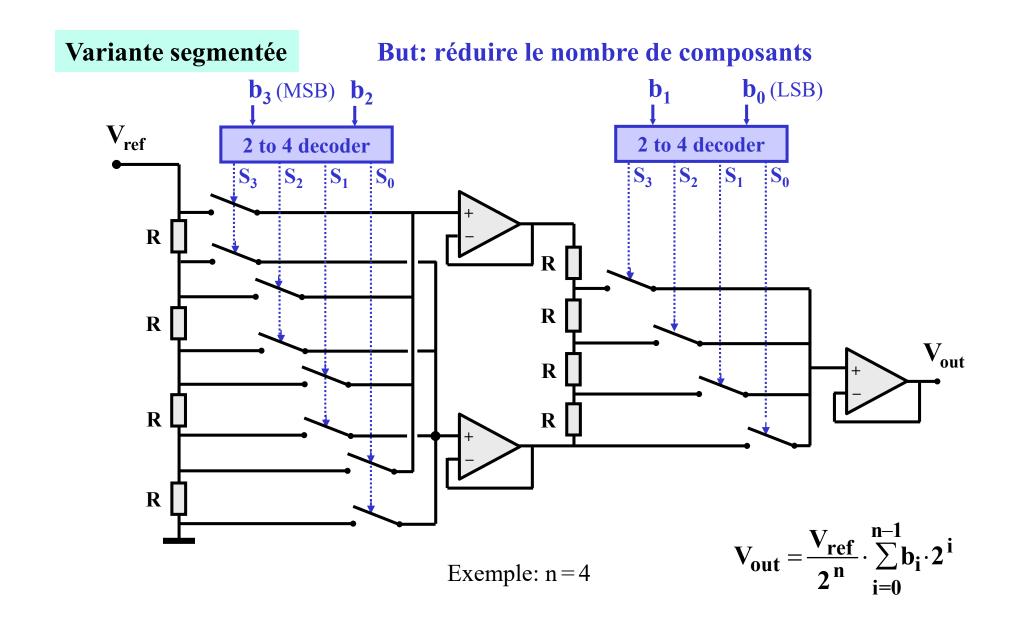

### 2.1. CONVERTISSEURS N/A POTENTIOMETRIQUES

### 2.1. CONVERTISSEURS N/A POTENTIOMETRIQUES

## 2.1. CONVERTISSEURS N/A POTENTIOMETRIQUES

#### Variante avec multiplexeur et logique de décodage

### 2.1. CONVERTISSEURS POTENTIOMETRIQUES

### 2.1 CONVERTISSEURS POTENTIOMETRIQUES

- © Les switches sont bien adaptés aux caractéristiques du transistor MOS, leur résistance n'influence pas la précision, mais seulement le temps de réponse

- © La monotonicité est garantie (sauf si segmenté)

- $\odot$  Pas d'erreur de gain: la dynamique de sortie est fixée par  $V_{ref}$

- Exemple: 8 bits => 256 résistances et 510 switches

ou 256 résistances et 256 switches + 256 portes AND

- **La segmentation réduit le nombre de composants, mais provoque des non-linéarités et peut engendrer une non-monotonicité**

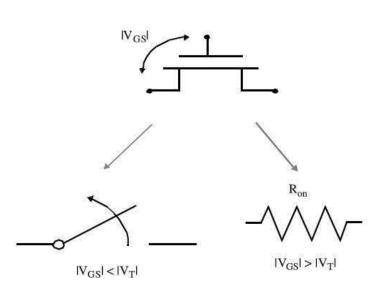

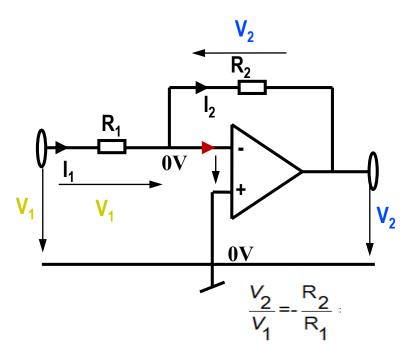

#### Elements de base dans les convertisseurs N/A

Switches en technologie CMOS

L'ampli op avec réaction négative (aussi suiveur de tension, sommateur)

Rappelez vous les '2 golden rules'

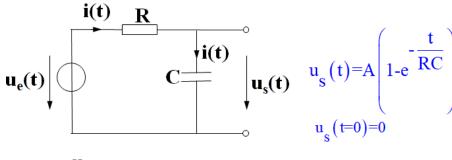

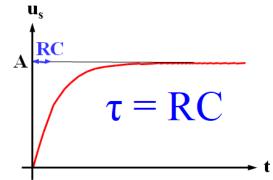

**Circuit RC**

La constante de temps τ caractérise la rapidité du circuit.

# 2.2. CONVERTISSEURS A RESISTANCES PONDEREES

#### 2.2. CONVERTISSEUR A RESISTANCES PONDEREES

# 2.2. CONVERTISSEUR A RESISTANCES PONDEREES

**②** Le nombre de résistances est limité à (n+1)

- **②** Les rapports élevés dans les valeurs de résistances sont difficiles à réaliser avec précision, et à maintenir en fonction du temps et de la température

- $oldsymbol{\otimes}$  La résistance parasite des switches  $r_{on}$  intervient en série avec les résistances utiles et limite également la précision

- © Les transistors MOS sont bien adaptés aux exigences des switches de ce circuit, ce qui n'est pas le cas des transistors bipolaires.

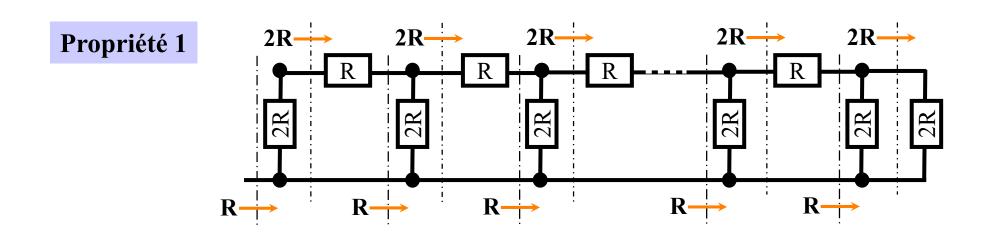

#### 2.3. CONVERTISSEURS: ECHELLE R/2R

### 2.3. CONVERTISSEURS: ECHELLE R/2R

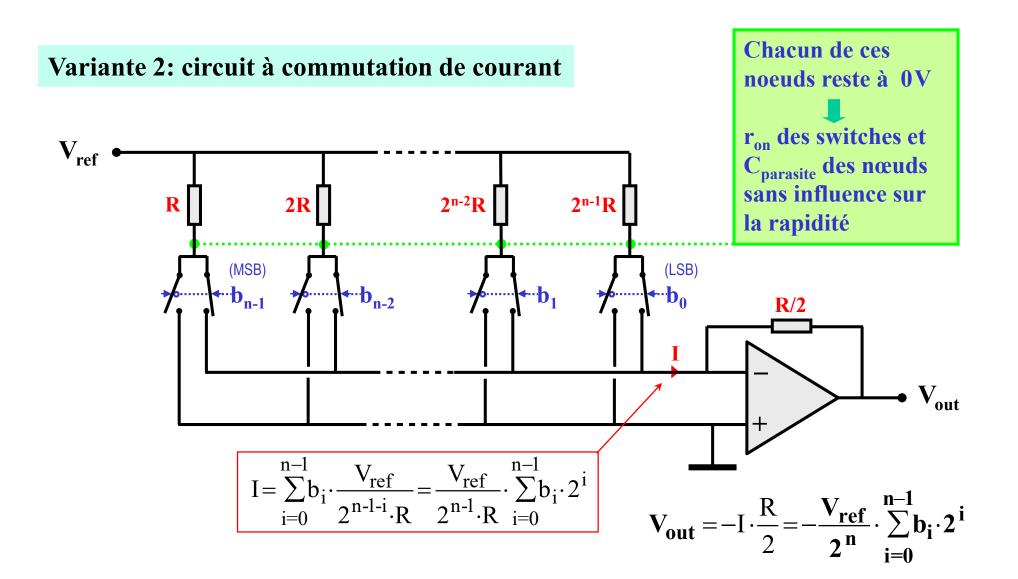

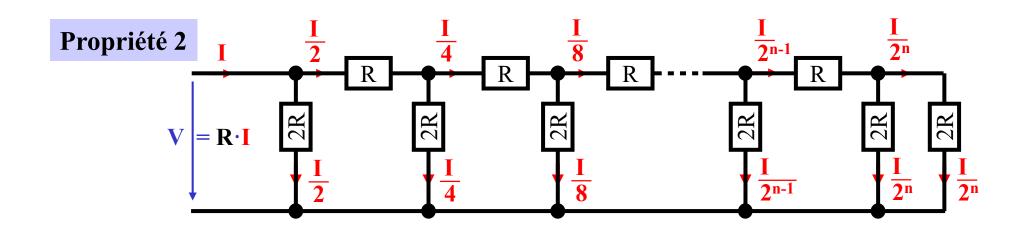

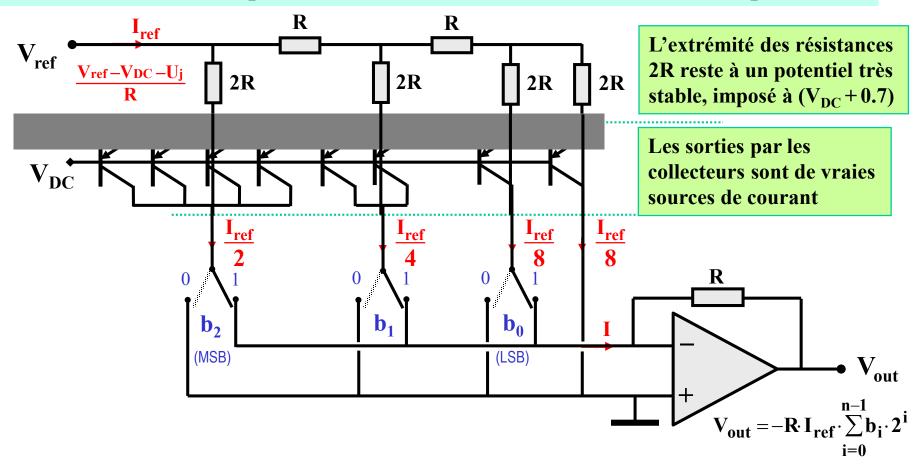

#### Convertisseur N/A à échelle R/2R et commutation de courant

- **©** Tous les nœuds sont à des potentiels fixes => rapidité

- $\otimes$   $V_{ref}$  et  $V_{out}$  de polarité opposée => alimentations + et nécessaires

### 2.3. CONVERTISSEURS: ECHELLE R/2R

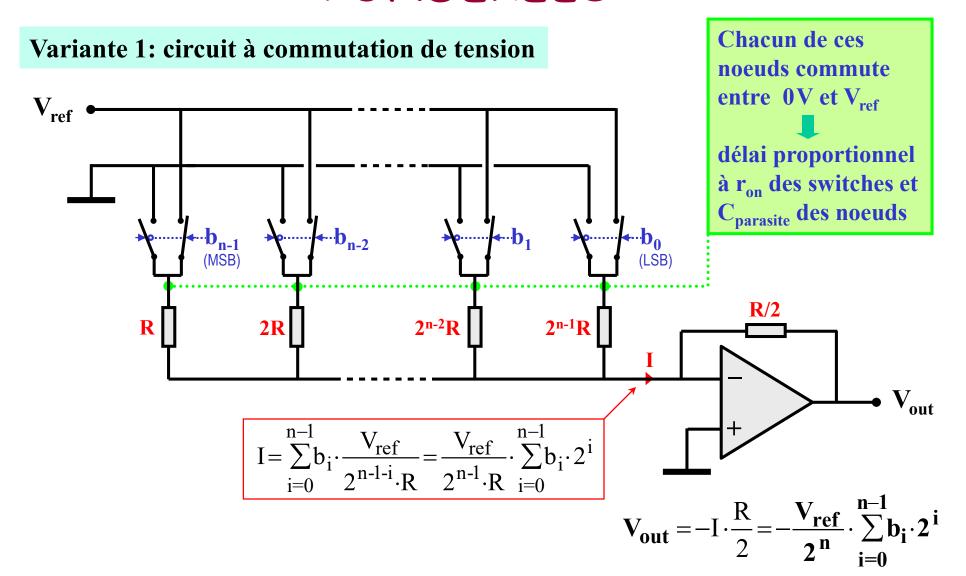

#### Convertisseur N/A à échelle R/2R inversée et commutation de tension

- **©** Tous les nœuds sont à des potentiels de même polarité => ce circuit peut fonctionner avec une seule alimentation

- **②** Vitesse limité par les constantes RC aux divers nœuds à des potentiels variables selon le code d'entrée

#### 2.3 CONVERTISSEURS: ECHELLE R/2R

- Le nombre de résistances est limité à (2n+2)

- Les rapports de résistances sont très précis et stables, car on emploie uniquement des résistances de valeur identique (2R = R + R)

- La résistance parasite r<sub>on</sub> des switches s'ajoute en série avec la résistance 2R des branches verticales, ce qui limite la précision.

- Il est toutefois possible d'avoir  $r_{on} << 2R$

- Les transistors MOS sont bien adaptés aux exigences des switches de ce circuit, ce qui n'est pas le cas des transistors bipolaires.

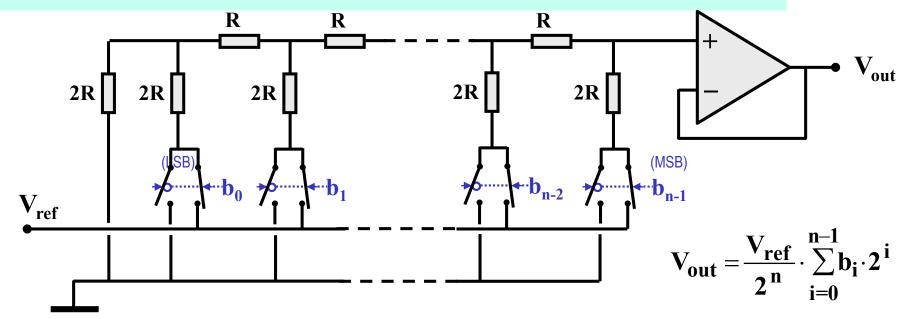

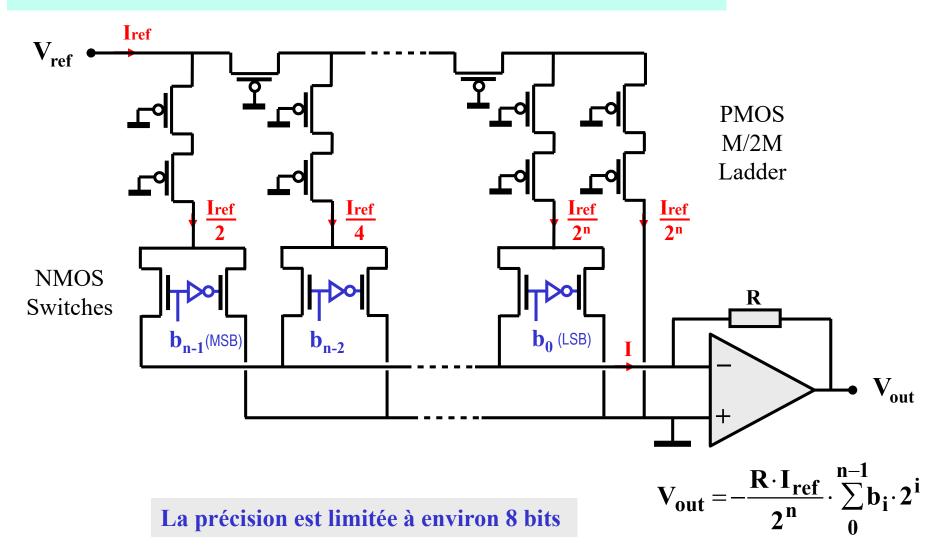

### 2.3. CONVERTISSEURS: ECHELLE M/2M

On obtient l'équivalent d'une échelle R/2R en remplaçant chaque élément R par un transistor PMOS

- © En technologie MOS, la solution M/2M occupe moins de surface que la solution R/2R, elle est donc plus économique.

- **②** La précision du rapport des courants est moindre qu'avec des résistances.

#### 2.3. CONVERTISSEURS: ECHELLE M/2M

#### Convertisseur N/A à échelle M/2M à commutation de courant

21

Principe avec charge passive

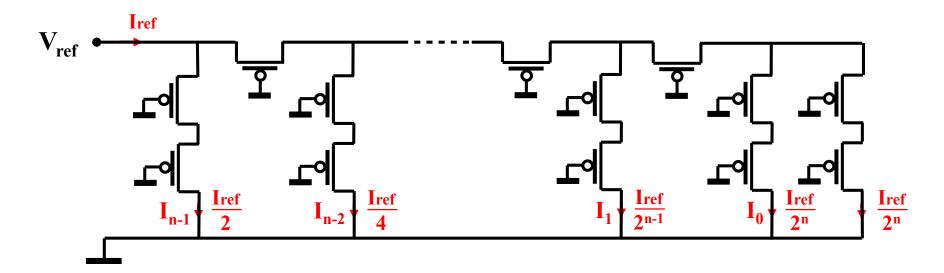

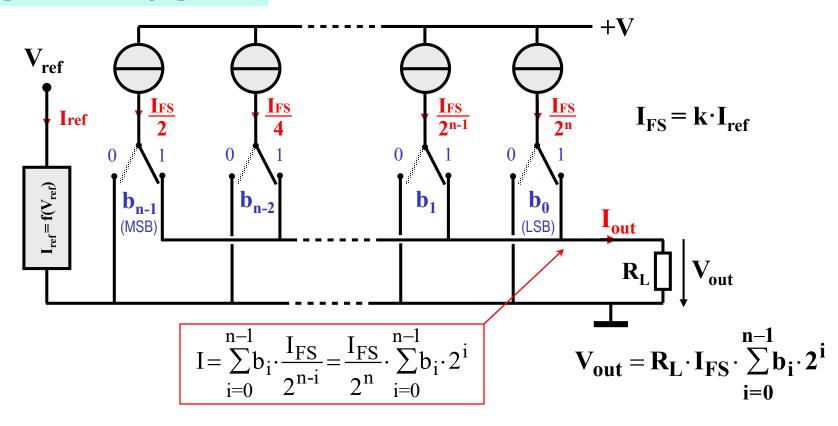

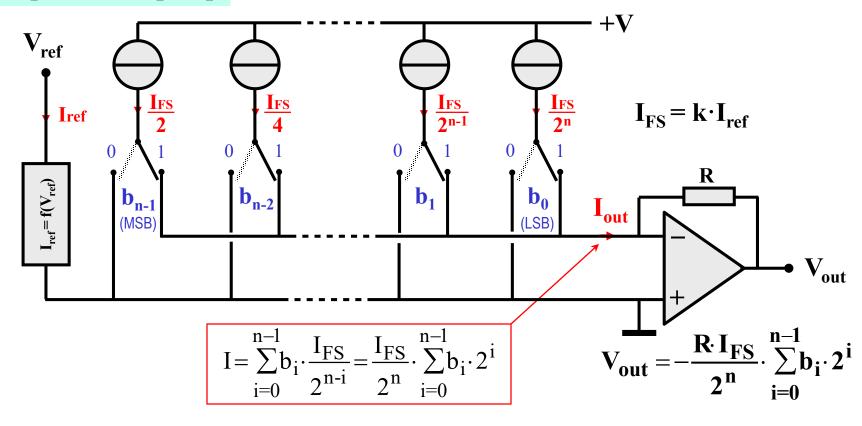

L'utilisation de sources de courant permet de s'affranchir du problème de la résistance parasite des commutateurs. Ceux-ci peuvent être réalisés à volonté avec des MOS ou des bipolaires.

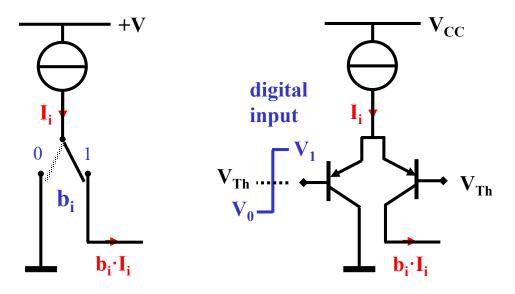

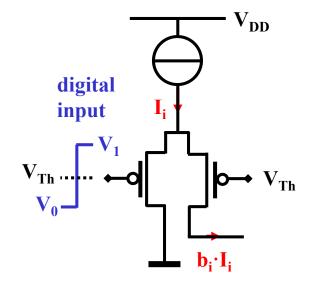

#### Aiguillages de courant

Une paire différentielle permet de réaliser un aiguillage de courant quasiparfait, rapide et indépendant des imperfections des transistors.

#### Principe avec ampli op

La résistance interne des sources n'a pas d'effet sur la précision.

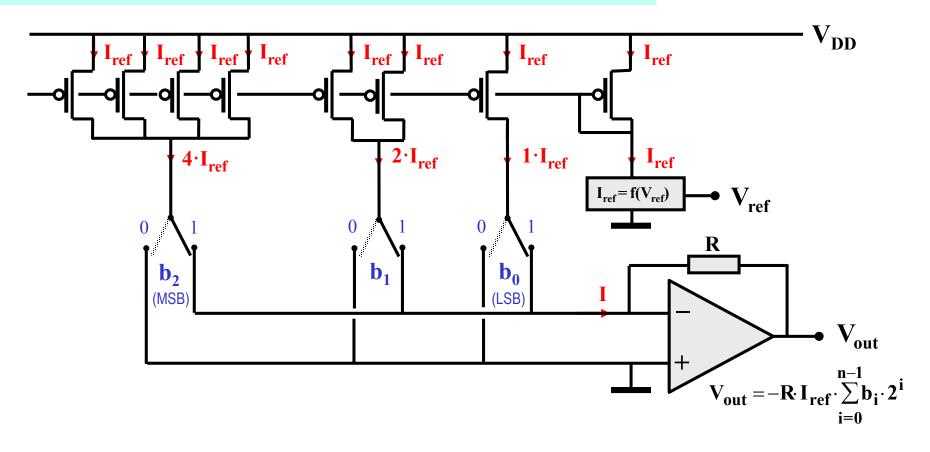

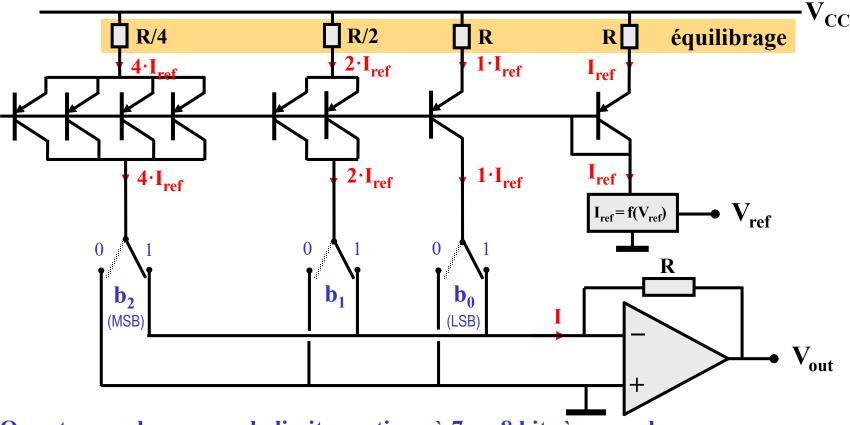

Convertisseur N/A MOS à sources de courant pondérées

Excellent convertisseur, simple à réaliser, mais limité aux environs de 8 bits par la surface prohibitive des blocs de transistors de rang supérieur.

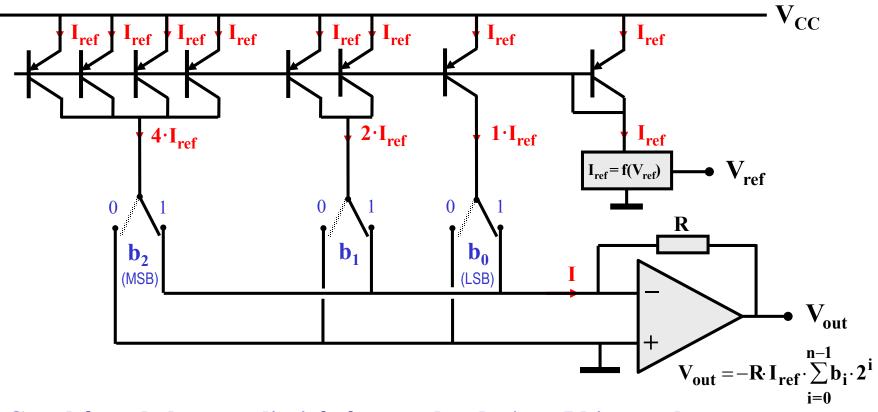

Convertisseur N/A bipolaire à sources de courant pondérées

Ce schéma de base est limitée à un ordre de 4 ou 5 bits par les imperfections d'appariement des transistors, dont le courant dépend exponentiellement de  $V_{\rm BE}\,.$

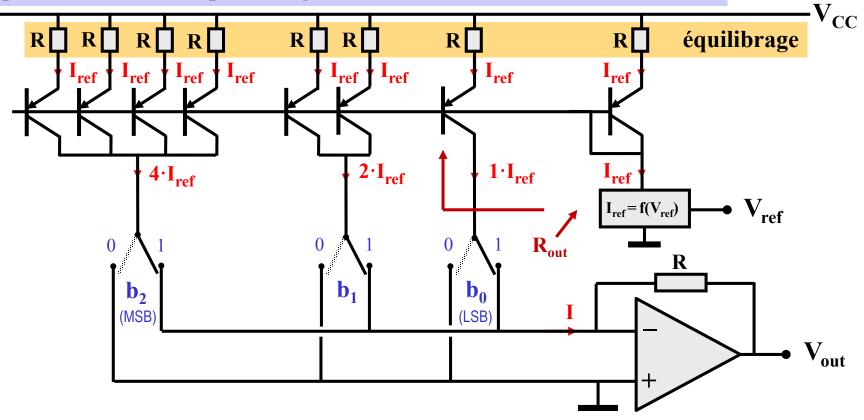

Convertisseur N/A bipolaire à sources de courant pondérées

Appariement amélioré par l'usage de résistances série dans les émetteurs

Ce schéma est limité en pratique à un ordre de 7 à 8 bits par la surface des transistors multiples et de leurs résistances.

Convertisseur N/A bipolaire à sources de courant pondérées

Appariement amélioré par l'usage de résistances série pondérées dans les émetteurs

On retrouve dans ce cas la limite pratique à 7 ou 8 bits à cause des erreurs d'appariement des résistances de valeurs pondérées selon les puissances de 2.

Convertisseur N/A bipolaire à échelle R/2R et sources de courant pondérées

Solution bipolaire de haute précision, limitée par la taille des transistors multiples. Cette limitation peut être contournée par la segmentation en 2 ou 3 tronçons.

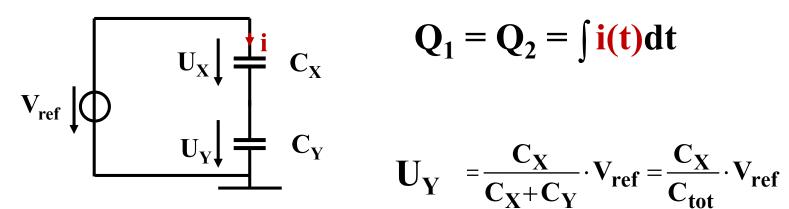

## Loi physique d'une capacité

$$U \downarrow \frac{1}{T} C \qquad q = C.u$$

$$dq/dt = C du/dt$$

$$i = C du/dt$$

$$\mathbf{Q}_1 = \mathbf{Q}_2 = \int \mathbf{i}(\mathbf{t}) d\mathbf{t}$$

$$\mathbf{U}_{\mathbf{Y}} = \frac{\mathbf{C}_{\mathbf{X}}}{\mathbf{C}_{\mathbf{X}} + \mathbf{C}_{\mathbf{Y}}} \cdot \mathbf{V}_{\mathbf{ref}} = \frac{\mathbf{C}_{\mathbf{X}}}{\mathbf{C}_{\mathbf{tot}}} \cdot \mathbf{V}_{\mathbf{ref}}$$

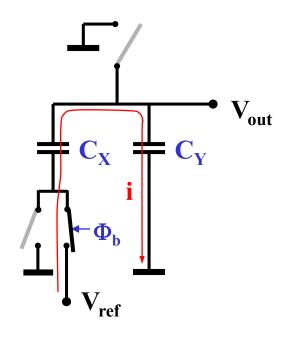

Variante 1: distribution passive de charge

Principe (1/2)

Phase a

Décharge de  $C_X$  et  $C_Y$  $V_{out} = 0$  et  $Q_X = Q_Y = 0$  Phase intermédiaire

Tous ouverts

Variante 1: distribution passive de charge

Principe (2/2)

Phase b

#### Au terme de la charge :

$$\mathbf{Q}_{\mathbf{X}} = \mathbf{C}_{\mathbf{X}} \cdot (\mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{out}})$$

$$\mathbf{Q}_{\mathbf{Y}} = \mathbf{C}_{\mathbf{Y}} \cdot \mathbf{V}_{\mathbf{out}}$$

Les 2 capacités ont été parcourues par le même courant i(t) durant toute la phase b

$$\mathbf{Q}_{\mathbf{X}} = \mathbf{Q}_{\mathbf{Y}} = \int \mathbf{i}(t) dt$$

$$C_X \cdot (V_{ref} - V_{out}) = C_Y \cdot V_{out}$$

$$\mathbf{V_{out}} = \frac{\mathbf{C_X}}{\mathbf{C_X} + \mathbf{C_Y}} \cdot \mathbf{V_{ref}} = \frac{\mathbf{C_X}}{\mathbf{C_{tot}}} \cdot \mathbf{V_{ref}}$$

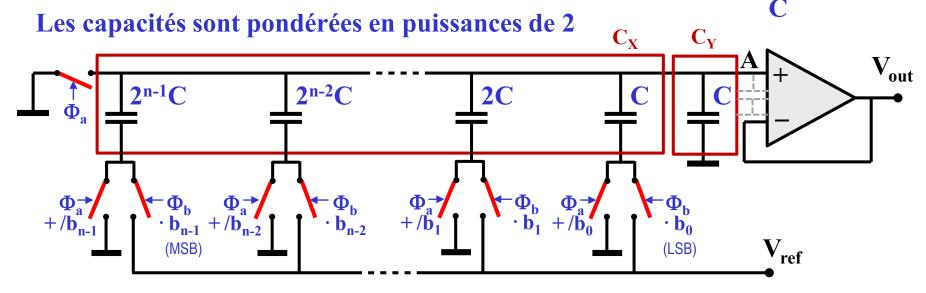

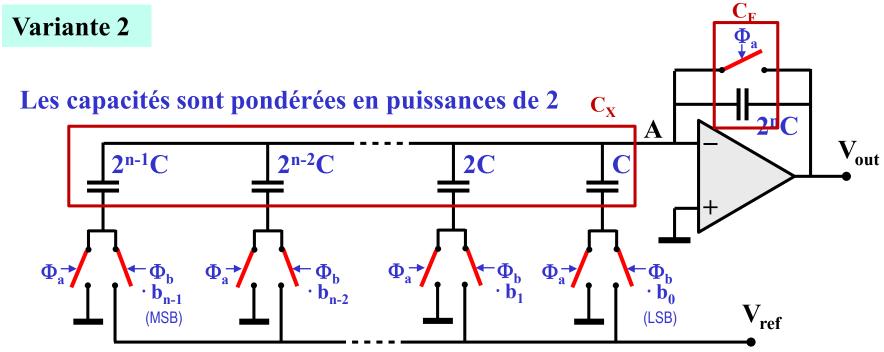

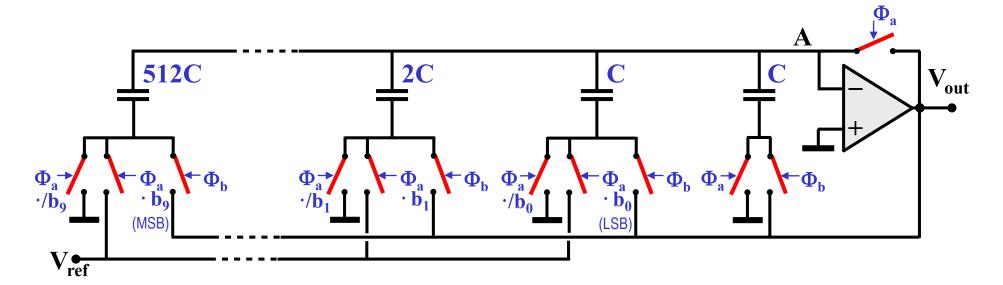

Variante 1: CNA à capacités pondérées et distribution passive de charge

En se référant aux capacités  $C_X$  et  $C_{tot}$  du circuit de principe, on a ici:

$$C_{X} = b_{0} \cdot C + b_{1} \cdot 2C + \dots + b_{n-2} \cdot 2^{n-2}C + b_{n-1} \cdot 2^{n-1}C$$

$$C_{tot} = C_{X} + C_{Y} = C + C + 2C + \dots + 2^{n-2}C + 2^{n-1}C = 2^{n}C$$

$$V_{out} = \frac{V_{ref}}{2^{n}} \cdot \sum_{i=0}^{n-1} b_{i} \cdot 2^{i}$$

**🗵 Influence de la capacité parasite globale au nœud A qui s'ajoute à C**tot

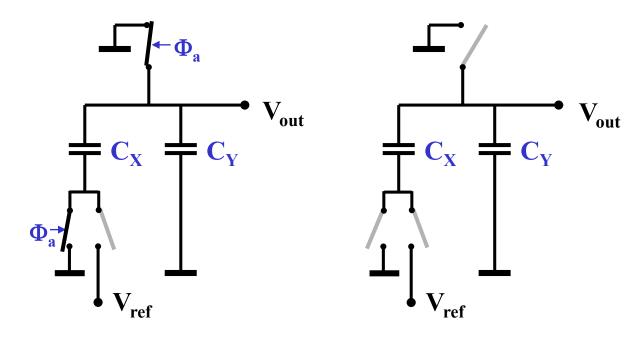

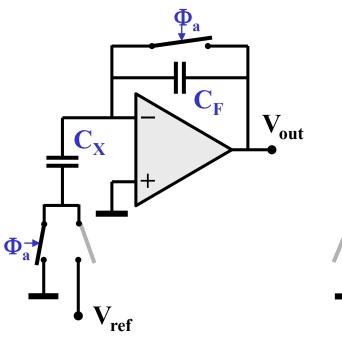

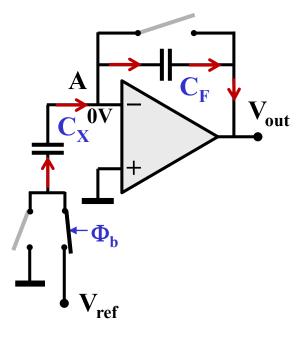

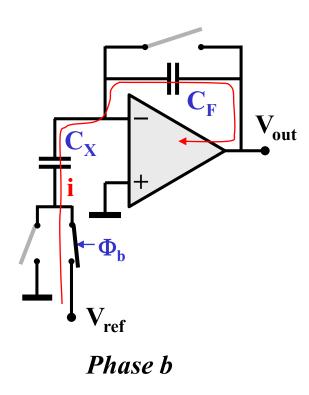

Variante 2: distribution active de charge

Principe (1/2)

Phase a

Décharge de  $C_X$  et  $C_Y$

Phase intermédiaire

Tous ouverts

Phase b

Charge par  $V_{ref}$  de  $C_X$  et par l'AO de  $C_Y$

Variante 2: distribution active de charge

Principe (2/2)

Au terme de la charge :

$$\mathbf{Q}_{\mathbf{X}} = \mathbf{C}_{\mathbf{X}} \cdot \mathbf{V}_{\text{ref}}$$

$$\mathbf{Q}_{\mathbf{F}} = \mathbf{C}_{\mathbf{F}} \cdot (-\mathbf{V}_{\mathbf{out}})$$

Les 2 capacités ont été parcourues par le même courant i(t) durant toute la phase b

$$\mathbf{Q}_{\mathbf{X}} = \mathbf{Q}_{\mathbf{F}} = \int \mathbf{i}(\mathbf{t}) \mathbf{dt}$$

$$\mathbf{C}_{\mathbf{X}} \cdot \mathbf{V}_{\mathbf{ref}} = -\mathbf{C}_{\mathbf{F}} \cdot \mathbf{V}_{\mathbf{out}}$$

$$\mathbf{V}_{out} = -\frac{\mathbf{C}_{\mathbf{X}}}{\mathbf{C}_{\mathbf{F}}} \cdot \mathbf{V}_{ref}$$

En se référant aux capacités  $C_X$  et  $C_F$  du circuit de principe, on a ici:

- © Insensible à la capacité parasite globale au nœud A qui est à un potentiel est

- **Mais capacité totale, donc surface de Si, double à cause de C**<sub>F</sub>

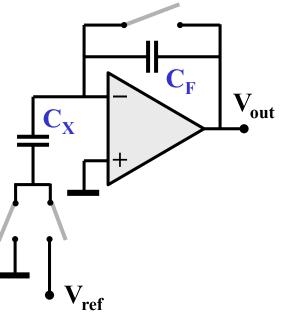

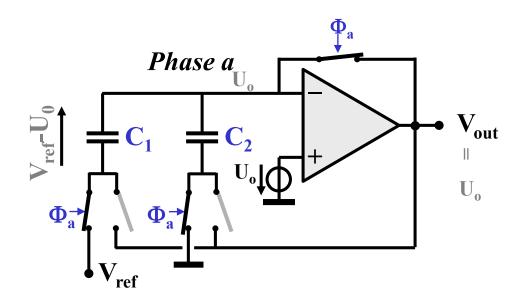

Variante 3

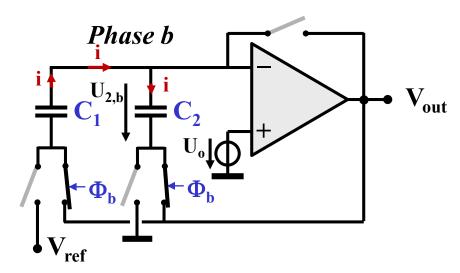

Principe (1/2)

$$\mathbf{U}_{2,b} = -\mathbf{V}_{\text{ref}} \cdot \frac{C_1}{C_1 + C_2} + \mathbf{U}_0 \qquad \qquad \mathbf{V}_{\text{out}} = -\mathbf{V}_{\text{ref}} \cdot \frac{C_1}{C_1 + C_2}$$

Phase a

Initialisation  $C_1$  chargée à  $V_{ref}$   $C_2$  déchargée

Phase intermédiaire non-représentée Tous ouverts

$\begin{array}{c} Phase \ b \\ On \ connecte \ la \ borne \\ inférieure \ de \ C_1 \ et \ C_2 \ \grave{a} \\ V_{out} \end{array}$

Variante 3, dite "Flip Around"

Schéma

- © Insensible à la capacité parasite totale au nœud X qui reste à un potentiel nul

- © Surface totale des capacités réduite de moitié

- Convertisseurs bien adaptés à la technologie CMOS : capacités de haute qualité + switches de haute qualité

- La résistance parasite des switches n'influence pas la précision, mais seulement la vitesse de conversion

- La précision est limitée aux environs de 10 bits par:

- la précision des rapports de capacités

- le phénomène d'injection de charge (injection d'horloge) par les interrupteurs MOS